「Hybrid Bonding:半導體產業未來發展中值得關注的重要技術」

在摩爾定律的發展上,Lithography (曝光) 一直是半導體產業中一個很重要的技術,因為晶片線寬尺寸的微縮,都是靠Lithography技術的進化而達成。

不過,在後摩爾時代,晶片設計的哲學有了一些改變。

後摩爾時代,除了微縮,晶片堆疊變成是增加電晶體數量的一個重要手段,而Bonding (鍵合) 技術,就變成達成晶片堆疊的一個重要手段,甚至可以說是關鍵。

因為,不管是Bonding的線寬,或是能耗,都會間接決定整個晶片系統性能的上限。

所以,我們今天就來聊一下這個在半導體產業越來越重要的技術:Hybrid Bonding。

(1). AI系統和後摩爾時代的需求:算力堆疊&晶片間的資料傳輸

我們都知道,近期AI相關晶片的需求提升得非常快。

而因為大型語言模型的關係,單一模型基本上沒有辦法裝到單一晶片裡。因此,AI相關晶片就逐漸演化成系統化的設計。

而在AI系統裡,通常會有不少的運算晶片,如CPU、GPU、ASIC…..等。也會有記憶體晶片,如HBM (High Bandwidth Memory)。

而當我們想要提升AI系統的性能、降低能耗時,我們會發現系統設計者會慢慢的將一些需要較大量資料溝通的晶片越放越近。

如原本是在PCB板上的兩個晶片,可能會放到載板上拉近距離,甚至是直接用2.5D或是3D封裝串接。

而這樣的串接,除了能夠拉近兩個晶片的距離而加速傳輸速度外,也會因為經過導線的距離大幅縮短而降低能耗。

在系統能耗越來越重要的時代,先進封裝就扮演了一個越來越重要的角色。

(2). 封裝技術的演進:從Wire Bonding到Hybrid Bonding

因此,封裝技術這幾年一直快速的往先進封裝的方向走,從Wire Bonding,到Die Bonding,甚至到Hybrid Bonding。

一開始,因為先進封裝的需求還不高,因此,基本上用Wire Bonding或是Flip Chip的封裝就能滿足。

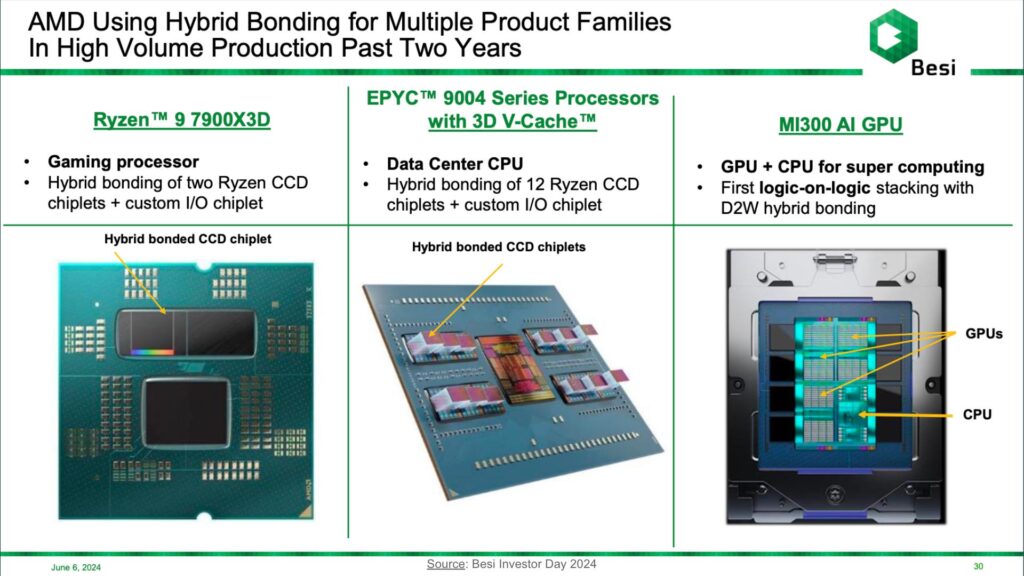

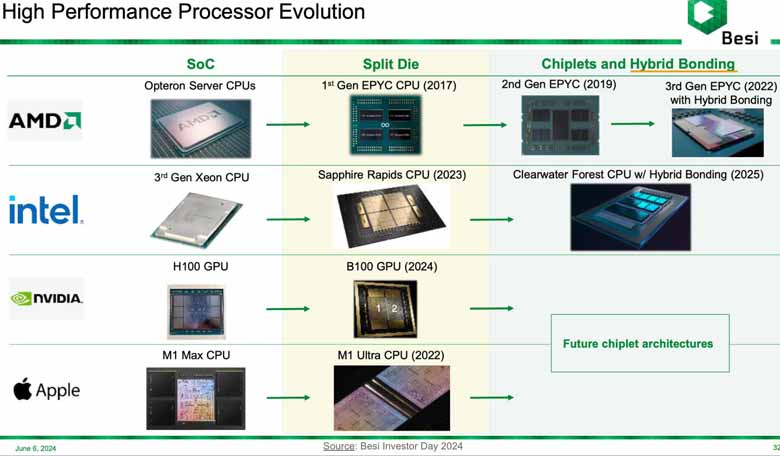

但這幾年來,AI系統對算力的需求大爆發,因此可以看到各家大廠都開始瘋狂的堆疊晶片在AI系統裡,以解決摩爾定律微縮趕不上算力需求的情況。

當算力以及能耗的要求越來越高時,越來越高級的封裝技術就被放進AI晶片系統的封裝裡。

如2.5D封裝會用到Micro bump技術,而需要更高記憶體和CPU/GPU資料傳輸速度的系統,就會導入3D的Hybrid Bonding技術。

(3). Hybrid Bonding技術不只用在Logic晶片堆疊,也用在各個領域上

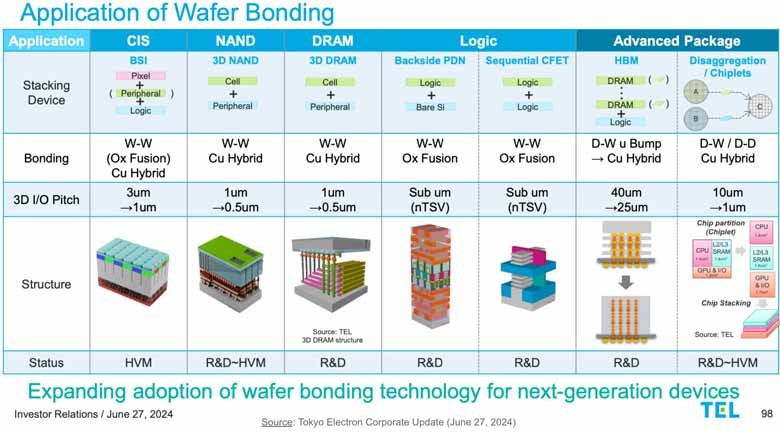

所以我們會發現,目前各個領域都開始導入Hybrid Bonding技術。

除了我們前面講的3D封裝會用到Hybrid Bonding技術以外,CMOS Image Sensor (CIS)、3D NAND、HBM……等領域都會用到Hybrid bonding技術。

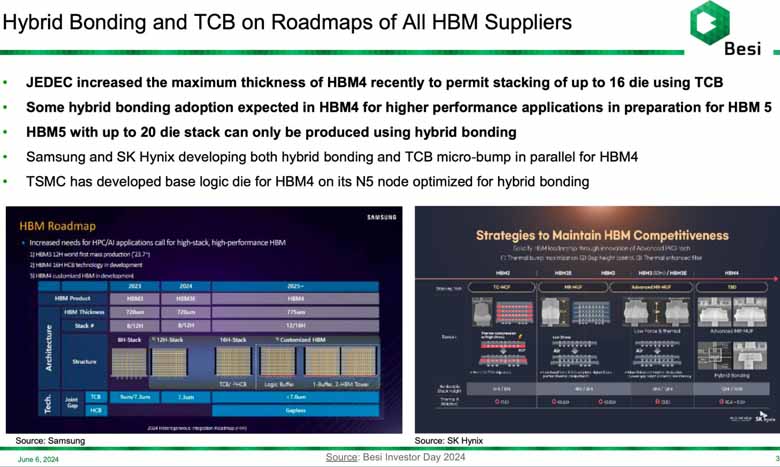

接下來HBM 4 (High Bandwidth Memory 第四代) 有可能會部分導入Hybrid Bonding,而HBM 5基本上是需要用Hybrid Bonding才能達到其性能上的需求。

所以我們知道,Hybrid Bonding其實比較像是各種領域的製造技術底層,這種能夠銜接不同晶片或模塊,且能大幅度提高資料傳輸速度的封裝技術,我們相信,其重要性應該會越來越高。

(4). Hybrid Bonding技術對未來AI系統的重要性

而Hybrid Bonding技術在目前市面上的AI晶片裡的使用雖然還算少數,但由於:

<a>. 未來算力需求會驅動更多晶片堆疊,晶片間的資料傳輸要求也會大幅提升

<b>. 多晶片系統的系統能耗需要更有效率

因此,我們相信Hybrid Bonding技術將會在AI晶片的系統裡面扮演一個非常重要的角色,不管是在3D封裝,還是在新一代HBM的製造上。

我們也可以從AMD的AI GPU發展上,看到這樣的趨勢 (MI300以及接下來的下一代晶片)

所以,我們覺得Hybrid Bonding將會是一個非常值得關注的技術。也期待看到更多這方面相關的技術發展。

另外,不管是IC設計的發展、先進製程、先進封裝領域,都會有不少像這樣子的重要技術。我們覺得,透過瞭解這些關鍵技術和其發展趨勢,大家能夠更好地去理解半導體產業未來可能會發展的方向和趨勢。

不過,因為半導體產業從上中下游有很多重要的技術和趨勢,要整理起來其實會需要很多工夫。所以,為了幫助大家,我們將一些較關鍵的技術趨勢整理起來,變成「2024半導體關鍵技術及趨勢」的線上課程。

如果你對半導體產業接下來的一些重要技術趨勢有興趣,想有一個整體性理解的話,我們會將這些關鍵的技術幫大家做系統性的整理,歡迎有興趣的版友參加~

在這個線上課程裡,我們會對下面的這些議題做更多的探討,如:

a. 半導體發展的變化造成IC設計思維的變化

b. System Scaling

c. 先進製程的發展

d. EUV & High NA EUV

e. Design Technology Co-Optimization (DTCO)

f. 晶片系統重構&先進封裝

- 報名連結:

https://www.redef.tech/featured-workshop/workshop-t1

講者:前ASML荷蘭總部產品經理和資深研發Vince Liu